|

|||

|

Page Title:

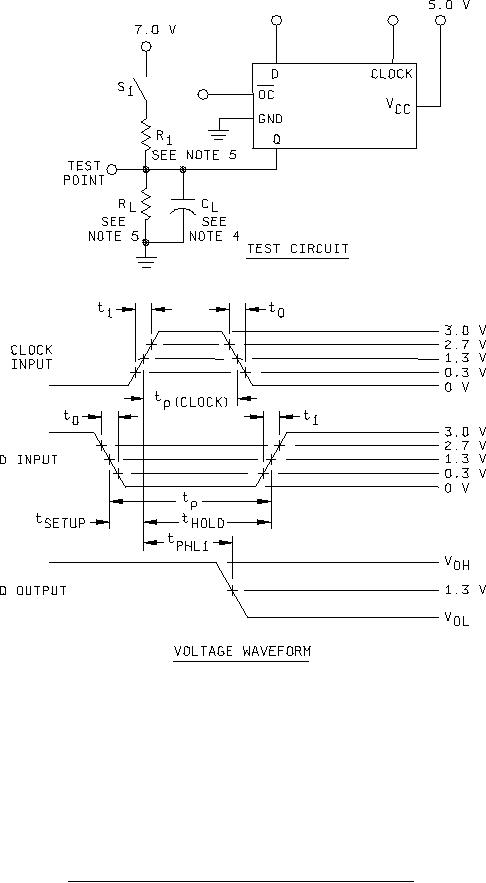

Figure 5. Synchronous switching test circuit (low level data) type 04 |

|

||

| ||||||||||

|

|  MIL-M-38510/372B

NOTES:

1. Clock input pulse characteristics: t1 = t0 = 6 1.5 ns; tP(CLK) = 16.5 ns; PRR ≤ 1.0 MHz.

2. D input pulse characteristics: t1 = t0 = 6 1.5 ns; t(SETUP) = 10 ns; t(HOLD) = 4 ns; tP = 14 ns;

PRR is 50% of clock PRR.

3. Inputs not under test are at ground.

4. CL = 50 pF 10%, including scope probe, wiring, and stray capacitance without package in test fixture.

5. RL = R1 = 499Ω 1%.

6. Voltage measurements are to be made with respect to network ground terminal.

FIGURE 5. Synchronous switching test circuit (low level data) type 04 - Continued.

20

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |