|

|||

|

Page Title:

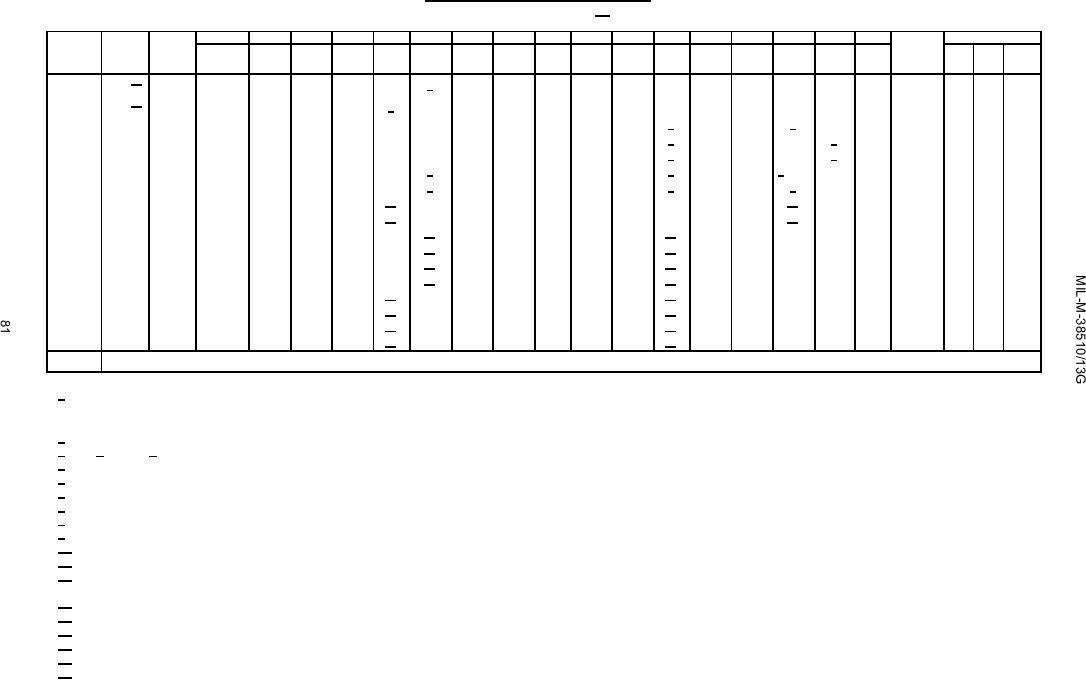

Table 3. Group A inspection for device type 08-cont. |

|

||

| ||||||||||

|

|  TABLE III. Group A inspection for device type 08 Continued.

Terminal conditions 17/

Case E, F

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Test limits

MIL-

Output

Output

Count

Count

Output

Output

Data D

Data C

Meas.

Subgroup

Symbol

Data B

Carry

Borrow

Clear

Data A

STD-883

Input

Output

Output

Input

Input

QB

QA

QC

QD

Test No.

Down

Up

GND

Input

Input

terminal

Min

Max

Unit

VCC

method

Load

14/

10

Fig 9A

134

OUT

2.4 V

4/

GND

2.4 V

GND

5.0 V

20

MHz

FMAX

QA

14/

Fig 9A

135

"

4/

2.4 V

"

2.4 V

GND

"

20

MHz

TC =125C

FMAX

QA

5/

5/

2.4 V

"

3

57

ns

Fig 9

136

"

GND

GND

"

tPHL7

QA

Fig 9

137

"

GND

GND

"

6/

GND

6/

"

"

"

tPLH8

66

QA

Fig 9

138

"

GND

GND

"

7/

GND

7/

"

"

62

"

tPHL8

QA

8/

"

2.4 V

GND

8/

OUT

8/ GND

GND

"

Carry

"

39

"

Fig 9A

139

GND

2.4 V

tPHL9

"

140

"

2.4 V

9/

"

2.4 V

"

9/

OUT

9/

"

"

Carry

"

45

"

tPLH9

"

141

"

10/

2.4 V

"

GND

"

2.4 V

OUT

10/

"

"

Borrow

"

39

"

tPHL10

"

142

"

11/

2.4 V

"

GND

"

2.4 V

OUT

11/

"

"

Borrow

"

42

"

tPLH10

"

143

GND

OUT

2.4 V

15/

"

GND

GND

15/

GND

GND

"

"

63

"

tPLH11

QA

"

"

144

GND

OUT

2.4 V

15/

"

GND

GND

15/

"

2.4 V

"

"

63

"

QB

"

"

145

2.4 V

2.4 V

15/

OUT

"

GND

GND

15/

"

2.4 V

"

"

63

"

QC

"

"

"

146

2.4 V

2.4 V

15/

OUT

"

GND

2.4 V

15/

"

2.4 V

"

"

63

QD

"

147

GND

16/

2.4 V

OUT

"

2.4 V

GND

16/

"

GND

"

"

71

"

tPHL11

QD

"

"

148

GND

16/

2.4 V

OUT

"

GND

2.4 V

16/

"

GND

"

"

71

"

QC

"

"

149

2.4 V

OUT

16/

2.4 V

"

GND

GND

16/

"

GND

"

"

71

"

QB

"

"

150

GND

OUT

16/

2.4 V

"

GND

GND

16/

"

2.4 V

"

"

71

"

QA

11

Same tests, terminal conditions, and limits as subgroup 10, except TC = -55C.

1/

Output voltages shall be either:

(a) H = 2.4 volts minimum and L = 0.4 volt maximum when using a high speed checker double comparator, or

(b) H ≥1.5 volts and L <1.5 volts when using a high speed checker single comparator.

2/

Only a summary of attributes data is required.

3/

A >2.0 V, B <0.8 V. Input voltages shown are the maximum for VIL and the minimum for VIH.

4/

See figure 9A. Apply waveform E for tests 117 and 134, and waveform H for tests 118 and 135.

5/

See figure 9, waveforms A, B, C, and D. Load AIN, then apply waveform A and observe the drop in QA output.

6/

See figure 9, waveforms B, C, and D. Load AIN, and observe tPLH of waveform D at output QA.

7/

Repeat steps as in note 6. Observe the pulse delay of the drop in QA when the load pulse is applied.

8/

See figures 9 and 9A, waveforms A, B, C, E, F, and G. First use clear pulse, then load pulse, then one count up pulse. Also see figure 9A, note 4.

9/

See note 5, add one more count up pulse for tPLH9 as shown on figure 10A, waveforms F and G.

10/

See figures 9 and 9A. First clear pulse, then one count down pulse.

11/

See note 7. Clear pulse first, figure 9 waveforms A, B, and C, add one more count down pulse for tPLH10 as shown on figure 9A, waveforms J and K.

12/

See figures 9 and 9A. First a clear pulse, then one count up pulse for QA. On next three tests enter count up pulses to appropriate count to

check QB, QC, and QD.

13/

See figure 9A waveforms H and J. On next three tests enter count down pulse, waveform H and observe tPHL11, waveform J on outputs QC, QB, and QA.

14/

FMAX, minimum limit specified is the frequency of the input pulse. The output frequency shall be one-half of the input frequency.

15/

Load pulse before count up input, then 4.5 V.

16/

Load pulse before count down input, then 4.5 V.

Terminal conditions (pins not designated may be H ≥ 2.0 V, or L ≤ 0.8 V, or open).

17/

18/

The limits shall be: -0.5 mA minimum, -1.3 mA maximum for circuit C, and -0.7 mA minimum, -1.6 mA maximum for all other circuits.

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |