|

|||

|

Page Title:

Table 3. Group A inspection for device type 09-cont. |

|

||

| ||||||||||

|

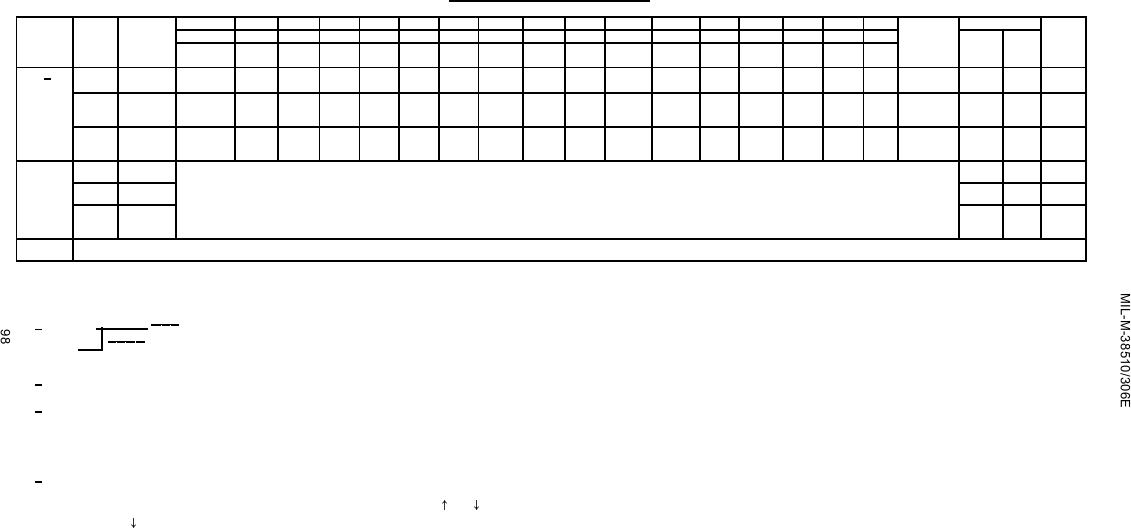

|  TABLE III. Group A inspection for device type 09- Continued.

Terminal conditions (pins not designated may be high ≥ 2.0 V; or low ≤ 0.7 V; or open).

Cases E,F

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

Test Limits

MIL-STD-

883

Subgroup

Symbol

Cases 2,X

2

3

4

5

7

8

9

10

12

13

14

15

17

18

19

20

Measured

Unit

method

Test no.

Ser. in

A

B

C

D

CLK

CLK

GND

CLR

E

F

G

QH

H

Shift

VCC

terminal

Min

Max

INHB

load

9 4/

fMAX

3003

76

GND

IN

GND

5.0 V

OUT

IN

GND

5.0 V

CLK to QH

25

MHz

Tc = 25C

tPHL5

See

77

"

IN

"

"

CLR to QH

5

40

ns

fig. 12

"

"

"

"

tPLH1

78

GND

IN

"

5.0 V

"

IN

GND

"

CLR to QH

"

31

ns

79

GND

IN

"

5.0 V

"

IN

GND

"

tPHL1

CLR to QH

"

35

ns

10

fMAX

20

MHz

Same tests and terminal as subgroup 9, except TC = 125C.

tPHL5

5

52

ns

5

40

ns

tPLH1

5

46

ns

tPHL1

Same tests, terminal conditions, and limits as subgroup 10, except TC = -55C.

11

NOTES:

1/ Apply

2.5 V minimum, 5.5 V maximum to clock input prior to test.

0V

2/ A = 2.5 V and B = 0.4 V.

3/ Output voltages shall be either:

a. H = 2.5 V minimum and L = 0.4 V maximum when using a high speed checker double comparator or,

b. H ≥1.5 V and L ≤1.5 V when using a high speed checker single comparator.

4/ fMAX minimum limit specified is the frequency of the clock input pulse. The output frequency

shall be one-half of the input clock frequency. The input frequency on the "H" shall be one-half

of the clock input frequency and the "H" shall be shifted such that the "H" and are coincident

with the clock . Rise and fall times ≤6 ns. Input peak voltage 3 to 5 volts.

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |