|

|||

|

|

|||

| ||||||||||

|

|  MIL-N-85005A(AS)

Access Signals - Panel switch positions shall be

3.5.2.4.2.2

interrogated at a cyclic rate. Immediate access signals to the NC

formed by actuating momentary action push-button indicators (PBI) (Para-

graph 3.5.2.5.3), shall be handled on an interrupt basis. The interrupt

request to the NC shall be on a dedicated line, and shall simultaneously

formulate an interrupt word in storage in the Keyer Control. When

the NC is ready to accept this interrupt word, a reset pulse is trans-

mitted followed by a command word requesting the Keyer Control to output

the stored interrupt word.

Serial Data Format - Serial data format between the

3.5.2.4.2.3

Keyer Control and NC shall be as presented in Figure 5.

Signal Inputs - Command reset input shall be a

3.5.2.4.2.4

differential logical "1" pulse of 250 50 ns duration. BIT status

lights input shall be separate dedicated lines:

Light illuminated.

"1"

=

Logical

Light extinguished.

"0"

=

Logical

(1) MALF

An input to light "CMPTR" shall also activate

(2) CMPTR

"MALF".

3.5.2.4.2.5

Command Word Serial Input - Command Word serial

input from NC to the Keyer Control shall be of serial format; character-

istics of Paragraph 3.5.2.4.1, waveform as shown in Figure 5, and struc-

ture as tabulated.

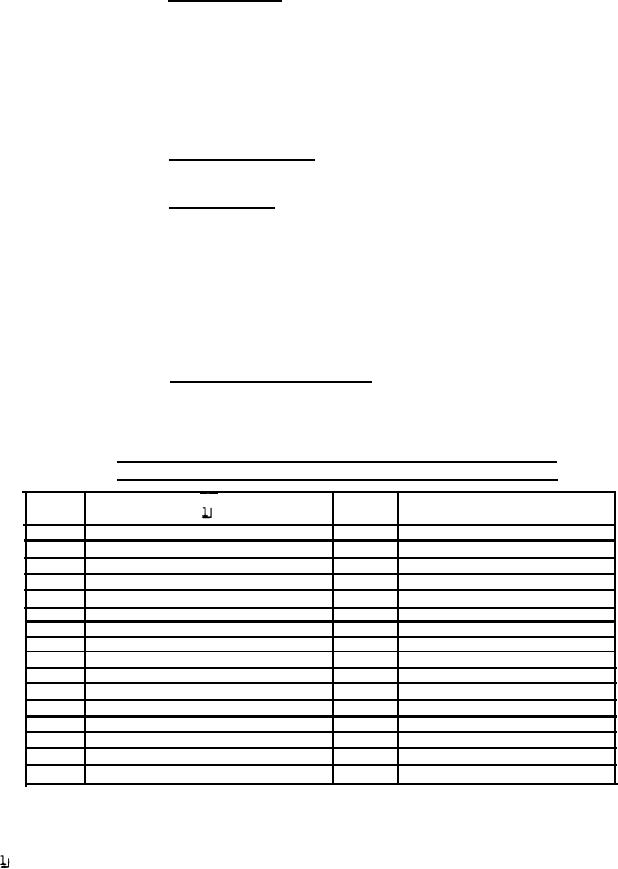

COMMAND WORD

MSB

LSB

15 14 13 12 11 10 9

87

6

54

3

210

Reference

No.

BIT

Paragraph

Table

Words

Function

1

3.5.2.4.3.3

INTERRUPT OUTGOING

0

3.5.2.4.3.4

1

1

KEYER CONTROL OUTGOING

SPARE

2

SPARE

3

4

SPARE

SPARE

5

SPARE

6

SPARE

7

SPARE

8

1

3.5.2.4.2.6

3

DIGITAL DISPLAY I INCOMING

9

1

2

3.5.2.4.2.7

DIGITAL DISPLAY II INCOMING

10

2

3.5.2.4.2.8

2

DIGITAL DISPLAY III INCOMING

11

12

2

3.5.2.4.2.9

2

DIGITAL DISPLAY IV INCOMING

1 and 2

3.5.2.4.2.10

2

KEYER CONTROL DISPLAY INCOMING

13

SPARE

14

3.5.2.4.2.11

1

KC LT INCOMING

15

A logical one shall indicate the related word sequence has been

commanded. Priority and sequence of processing shall progress from

bit 0 through bit 15 with bit 0 processing first.

Spare bits in the Command Word must be zero. When used in a word bit

identification, a spare bit is presently unused and future use is possible.

Hardware modification may be required for such future use.

- 27 -

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |