|

|||

|

|

|||

| ||||||||||

|

|  MIL-M-38510/231C

NOTES:

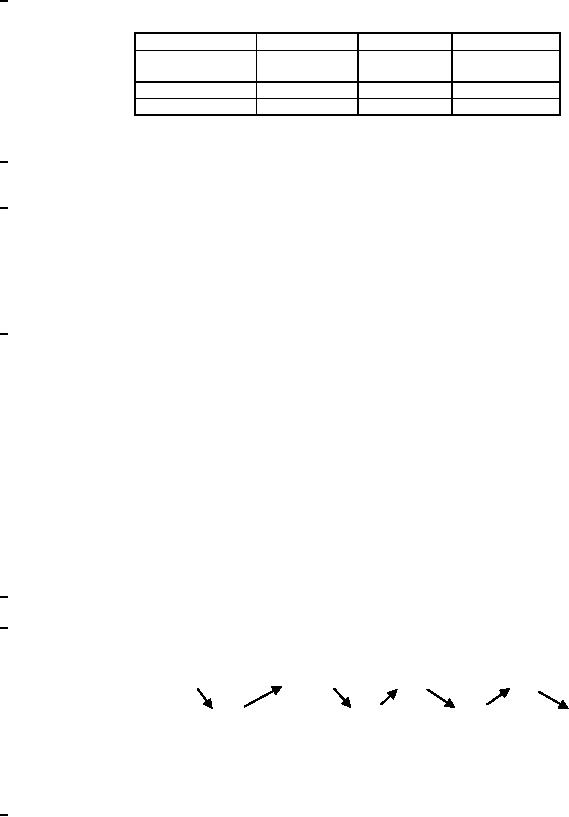

1/ The ICC are as follows:

25C

125C

-55C

Device type

01, 02, 05, 06,

155 mA

130 mA

170 mA

07, 08, 09, 10, 14

03, 04, 13

65 mA

55 mA

75 mA

11, 12, 15

80 mA

70 mA

90 mA

2/ Toggle from ≥ 3.0 V to 0.4 V and return.

3/ The functional tests shall verify the truth table of figure 3. All bits shall be tested. Terminal conditions shall be as

follows:

a.

Inputs: H = 2.4 V, L = 0.4 V.

Outputs: Output voltage shall be H ≥ 1.5 V and L < 1.5 V when using a high-speed checker single

b.

comparator.

c.

The functional tests shall be performed with VCC = 4.5 and VCC = 5.5 V.

4/ GALPAT. This program will test all bits in the array, the addressing and interaction between bits for ac

performance tAVQV, tSVQV, tSCQV, tWZQV, and tWHQV, the memory is initialized by writing a field of "H" and then a field of

"L".

Description:

1.

Write an "H" in word 0.

2.

Word 0 is read.

3.

Word 1 is read.

4.

Word 0 is read

5.

Word 2 is read.

6.

Word 0 is read.

7.

The reading procedure continues back and forth between word 0 and the next higher numbered word until

word 1024 is reached, then increments to the next word and reads back and forth as in steps 1 through 7

and shall include all words.

2

Pass execution time = (n + n) x cycle time. n = 1024.

8.

9.

The GALPAT tests shall be performed with VCC = 4.5 and 5.5 V.

5/ The outputs shall be loaded per load A of figure 5.

6/ Galloping Galwresh (with row column ping pong read GGII)

The Galloping Galwresh (GG) is started by first writing a field of zeros and then a field of ones into the memory

under test (MUT). The following sequence is then performed.

Test Bit

R "1"

Write "0"

R "0"

W "1"

Background bit

R "1"

R "1"

R "1"

R "1"

The background bits are read in ping-pong fashion in the Row/Column of the test bit. The sequence is repeated

for the next test bit (Y advancing X) until the test bit reaches Xmax Ymax. The inverse pattern is then performed

with VCC = 4.5 and 5.5 V.

7/ For device type 05 and 06, tWHAC and tAVWL = 10 ns.

59

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |