|

|||

|

Page Title:

Table 1. Electrical performance characteristics-cont. |

|

||

| ||||||||||

|

|  MIL-M-38510/653B

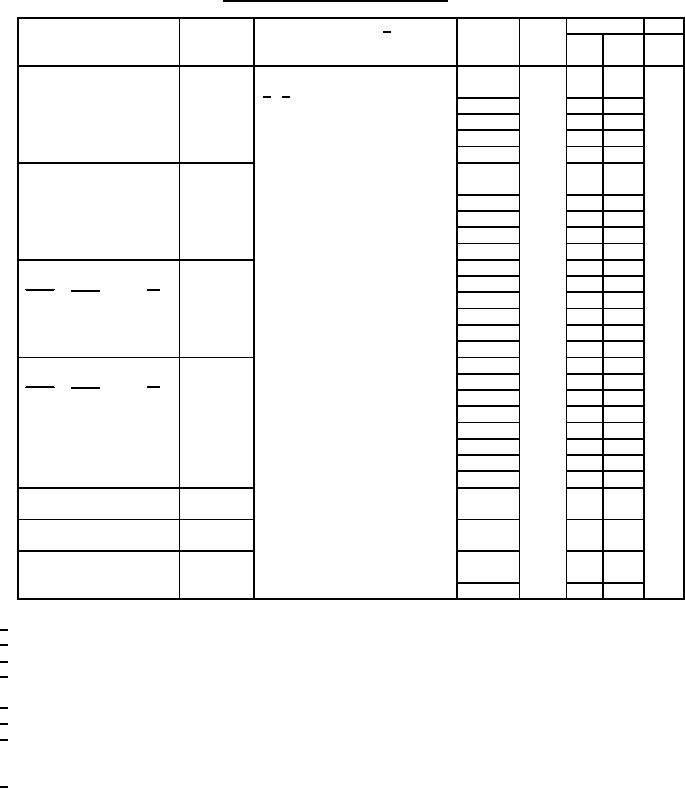

TABLE I. Electrical performance characteristics Continued.

Test

Symbol

Conditions 1/

Device

VCC

Limits

Unit

TC = +125C

type

Min Max

unless otherwise specified

CL = 50 pF 10%

4.5 V

ns

Propagation delay time,

tPLH1

02,04

5

41

low to high level,

05,52

7/ 8/

CLK to Q

01-03

5

40

06

6

47

07

5

42

08

4

41

Propagation delay time,

tPHL1

02,04

5

41

high to low level,

05,52

CLK to Q

01-03

5

40

06

6

47

07

5

42

08

4

41

Propagation delay time,

tPLH2

01,05

6

43

low to high level,

02

5

54

CLK or PRE to Q or Q

03

6

51

04

6

54

08

4

43

52

5

47

Propagation delay time,

tPHL2

01,05

6

43

high to low level,

02

5

54

CLK or PRE to Q or Q

03

6

51

04

6

54

06

5

41

07

5

42

08

4

43

52

5

47

06

5

35

Enable time to high or

tPZH or

low level

tPZL

06

5

35

Disable time to high or

tPHZ or

low level

tPLZ

Transition time,

tTLH or

01-05

3

20

low to high level

tTHL

07,08,52

or high to low level

06

2

16

1/

Complete terminal conditions shall be as specified in table III.

2/

Guaranteed but not tested.

3/

Total supply current = ICC + ICCĆ.

4/

IOZL sets internal D flip-flops to high state.

IOZH sets internal D flip-flops to low state.

5/

Power dissipation capacitance (CPD) per flip-flop.

6/

See the formula for determining maximum frequencies shown in table IA.

Tested at VCC = 4.5 V at +125C for sample testing and VCC = 4.5 V and +25C for screening.

7/

Guaranteed at other VCC voltages and temperatures. See tables IA and IB (as appropriate) and the

exception in 4.4.1d.

8/

For propagation and transition delay times at VCC = 2.0 V, increase limit by a factor of 5.

For propagation and transition delay times at VCC = 6.0 V, decrease limit by a factor of 0.85.

8

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |