|

|||

|

Page Title:

Table 3. Group A inspection for device type 03-cont. |

|

||

| ||||||||||

|

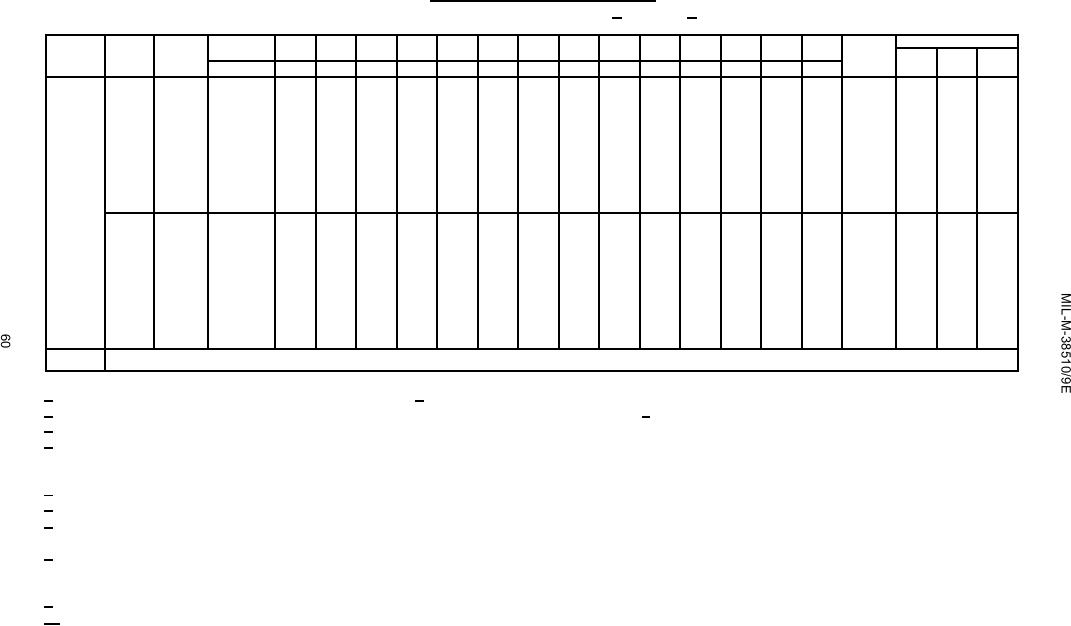

|  TABLE III. Group A inspection for device type 03 - Continued.

Terminal conditions (pins not designated may be H > 2.0 V or L < 0.8 V or open).

Cases

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Test limits

MIL-

A, B, C, D

Meas.

Subgroup

Symbol

STD-883

Min

Max

Unit

terminal

method

GND

CLK

CLR

Test No.

SIB

QA

QB

QC

QD

QE

QF

QG

QH

VCC

SIA

3003

198

IN

IN

OUT

GND

IN

4.5 V

5.0 V

10

42

ns

10

QA

tPLH2

"

(Fig 6)

199

"

"

OUT

"

"

"

"

"

"

"

TC = 125C

QB

"

"

"

"

"

"

200

"

"

OUT

"

"

"

"

QC

"

"

"

"

"

"

201

"

"

OUT

"

"

"

"

QD

"

"

"

"

"

"

202

"

"

"

"

"

OUT

"

QE

"

"

"

"

"

"

203

"

"

"

"

"

OUT

"

QF

"

"

"

'`

"

"

204

"

"

"

"

"

OUT

"

QG

"

"

"

'`

"

"

205

"

"

"

"

"

OUT

"

QH

"

206

"

"

OUT

"

"

"

"

"

52

"

"

QA

tPHL2

"

"

"

"

"

"

207

"

"

OUT

"

"

"

"

QB

"

"

"

"

"

"

208

"

"

OUT

"

"

"

"

QC

"

"

"

"

"

"

209

"

"

OUT

"

"

"

"

QD

"

"

"

"

"

"

210

"

"

"

"

"

OUT

"

QE

"

"

"

"

"

"

211

"

"

"

"

"

OUT

"

QF

'`

"

"

"

"

"

212

"

"

"

"

"

OUT

"

QG

"

"

"

'`

"

"

213

"

"

"

"

"

OUT

"

QH

11

Same tests, terminal conditions and limits as for subgroup 10, except TC = -55 C.

1/

A = normal clock pulse, except for subgroups 7 and 8 (see 3/).

2/

B = momentary GND, then 4.5 V to clear register prior to test, except for subgroups 7 and 8 (see 3/).

3/

For subgroups 7 and 8, A = VCC and B = GND.

4/

Output voltages shall be either:

(a) H = 2.4 V minimum and L = 0.4 V maximum when using a high speed checker double comparator, or

(b) H ≥ 1.5 V and L < 1.5 V when using a high speed checker single comparator.

5/ The tests in subgroups 7 and 8 shall be performed in the sequence specified.

6/ Only a summary of attributes data is required.

7/ For schematics incorporating 4.5 kΩ base resistors, the minimum and maximum limits shall be -0.6 and -1.5 mA, respectively.

For schematics incorporating 6 kΩ base resistors, the minimum and maximum limits shall be -0.4 and -1.3 mA, respectively.

8/ For device type 03, schematic circuits A, D, E and F, the minimum and maximum limits shall be -0.7 and -1.6 mA, respectively.

For schematic circuit B, the minimum and maximum limits shall be -0.8 and -2.6 mA, respectively.

For schematic circuit C, the minimum and maximum limits shall be -0.6 and -1.5 mA, respectively.

9/ For device type 03, schematics circuits A, C, D, E and F, the maximum limits shall be 40 A. For schematic circuit B, the maximum limits shall be 80 A.

10/ For device type 03, schematics circuits A, C, D, E and F, the maximum limits shall be 100 A. For schematic circuit B, the maximum limits shall be 200 A.

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |