|

|||

|

|

|||

| ||||||||||

|

|  MIL-N-8160K(AS)

Para 3.4.4.1f

(cont)

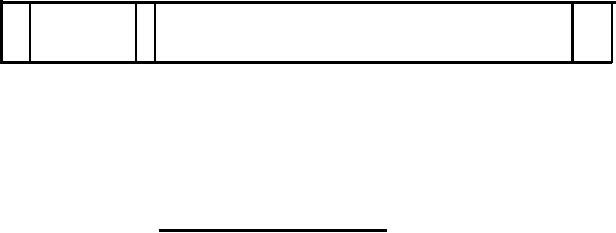

The particular word in memory to be loaded shall be

*

indicated by means of six label bits attached to

the transmitted data (see format in figure 8). Bit

1 (MSB of label) shall be loaded with a logic zero.

The ANCU or test equipment designed in accordance

with XAS-1233, or equivalent, may load data in any

sequence since the label will establish the 16 core *

locations into which the data are to be loaded.

When reading the memory data, the ANCU shall receive

*

sequenced data, labels 0 thru 31. The label bits

shall be determined by an address sequencer in the

IMU memory, which is reset to zero for a maximum

*

of 500 msec during power turn-on. Sequencing of

the data shall repeat after the block of 32 words

is transmitted. A parity bit shall be assigned such

that the total number of one's transmitted in bits

1 thru 22 is odd. Figure 9 presents the timing

diagram for the serial transfer of IMU calibration

data between the ANCU and IMU.

1234567891011

121314151617181920

2122

\

L

M

M

L

o SLABEL S s s

CALIBRATION DATA

s

P

B

B

B

B

BIAS AND SCALE FACTOR CORRECTION DATA WORD FORMAT

Note: S = sign bit (O = plus)

P = parity

Figure 8.

Calibration Data Word Format

(1) Calibration Data Clock - This clock input to

the IMU from the ANCU or test equipment designed

-

in accordance with XAS-1233, or equivalent,

*

shall be used for gating the calibration data

in and out of the IMU. Any clock rate less

than or equal to 250 KHz may be supplied to

the IMU. The pulse width of the clock shall

be greater than 200 nanoseconds. The ANCU

44

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |