|

|||

|

Page Title:

Logic Signal Inputs, Differential Type (LD/R) |

|

||

| ||||||||||

|

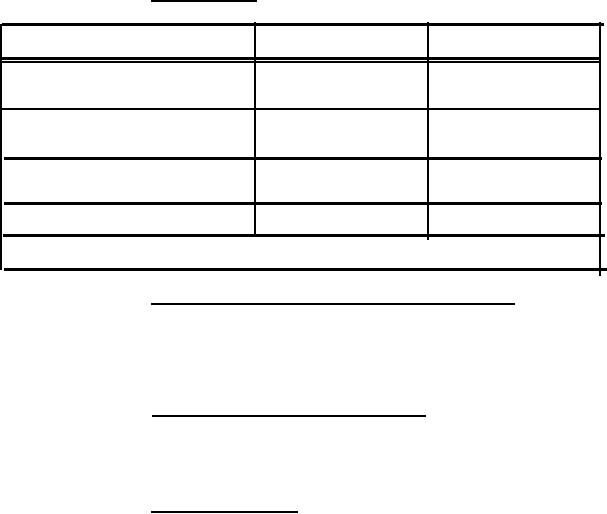

|  MIL-N-85005A(AS)

Power Sources - Logic and signal power sources shall

3.5.11.6.1

be as follows:

SIGNAL SOURCE

LOGIC POWER SOURCE

ANNUNCIATOR

SDC

NC (LD/R)

ALN (Align)

SDC

NC (LD/R)

NAV (Navigate)

SDC

NC (LD/R)

SLV (Slave)

N/A

Battery Unit (SW)

ATTD (Attitude)

IMS PS (SEL)

LMS PS

IMS FAIL

IMS GA (SEL)

CMPTR

NC (LD/R)

SDC

SEL = Single Ended Logic SW = Switch

LD/R = Line Driver/Receiver.

Logic Signal Inputs, Differential Type (LD/R) - All

3.5.11.6.2

differential logic input circuitry shall be similar to a differential

line receiver type A9615 and shall be compatible with the signal supplied

by a differential line driver similar to A9614. Input impedance shall

be nominal 130 ohms dc, balanced line load. Logic levels shall be as

defined in Figure 4.

Logic Signals, Single Ended (SEL) - Single ended

3.5.11.6.3

logic signals shall be unbalanced steady state signals as follows:

2.4 to 5.5 VDC

Logical one "1" =

0 to 0.4 VDC

Logical zero "0" =

Logic Requirements - Logic circuits shall be incorpor-

3.5.11.6.4

ated to control specific annunciators as follows:

The IMS FAIL annunciator shall illuminate when

either of the single ended logic (SEL) discretes, PS or GA, go to Zero

during the ALIGN, NAV, SLAVE and ATTD modes. The IMS FAIL annunciator

shall illuminate whenever logic power is lost during the ALIGN, NAV,

SLV, and ATTD modes. The ATTD annunciator shall illuminate upon a

switch closure signal input. This signal shall be inoperative during

the OFF, CMPTR, and ATTD modes.

The ALN, NAV, SLV, and CMPTR annunciators shall

illuminate whenever the logic signal input is "1" and shall be inopera-

tive whenever the logic power is lost.

- 116 -

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |