|

|||

|

Page Title:

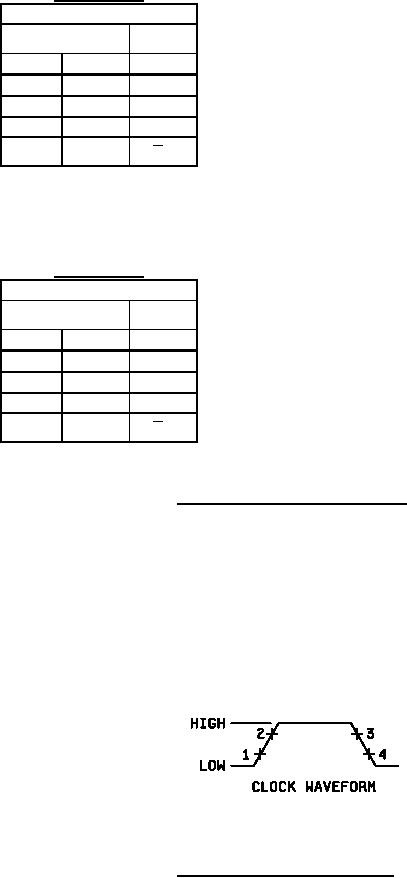

Figure 2. Truth tables and device descriptions device type 03 |

|

||

| ||||||||||

|

|  MIL-M-38510/21F

Positive logic:

Low input to clear sets Q to low level

Device type 03

Truth table

Clear is independent of clock

tn

tn+1

J

K

Q

NOTES:

L

L

Qn

1. tn = Bit time before clock pulse.

L

H

L

2. tn+1 = Bit time after clock pulse.

H

L

H

H

H

Qn

Device type 04

Positive logic:

Low input to preset sets Q to high level

Truth table

Low input to clear sets Q to low level

Preset and clear are independent of clock

tn

tn+1

J

K

Q

NOTES:

L

L

Qn

1. tn = Bit time before clock pulse.

L

H

L

2. tn+1 = Bit time after clock pulse.

H

L

H

H

H

Qn

Description for device types 03 and 04

These flip-flops are based on the master slave principle and each has AND gate inputs for entry into

the master section which are controlled by the clock pulse. The clock pulse also regulates the state of

the coupling transistors which connect the master and slave sections. The sequence of operation as

controlled by the clock pulse is as follows:

1.

Isolate slave from master.

2.

Enter information from AND gate inputs to master.

3.

Disable AND gate inputs.

4.

Transfer information from master to slave.

Figure 2. Truth tables and device descriptions- Continued.

11

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |