|

|||

|

Page Title:

Table 3. Group A inspection for device type 01-cont. |

|

||

| ||||||||||

|

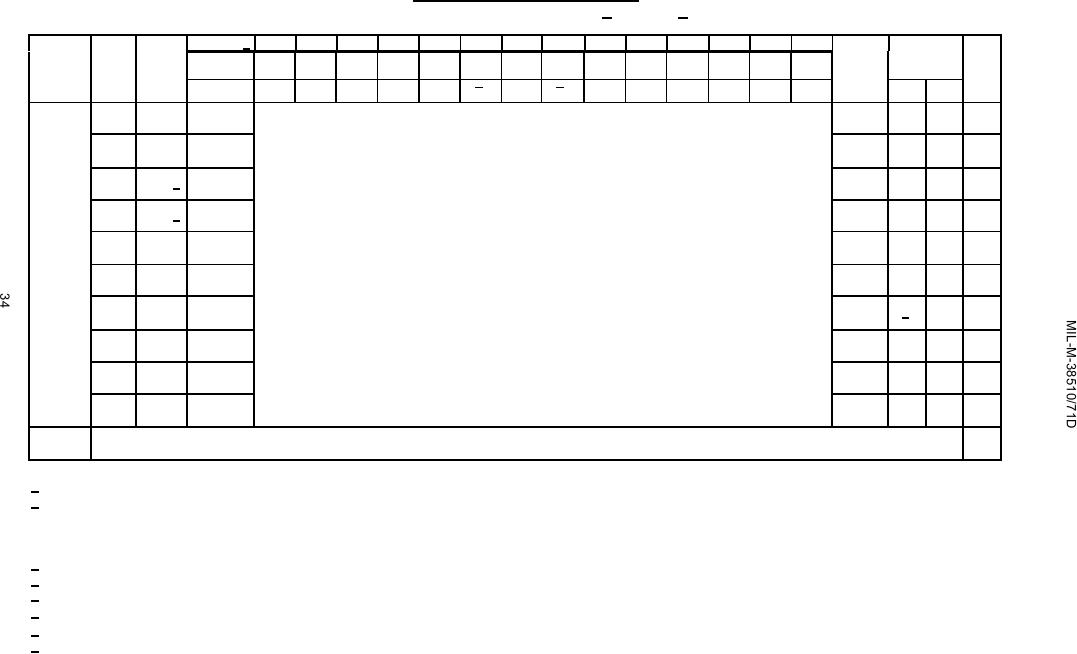

|  TABLE III. Group A inspection for device type 01 - Continued.

Terminal conditions (pins not designated may be high > 2.0 V, low < 0.8 V, or open).

Cases X, 2 1/

2

3

4

6

8

9

10

12

13

14

16

18

19

20

MIL-

Cases A,

1

2

3

4

5

6

7

8

9

10

11

12

13

14

Test limits

Subgroup

Symbol STD-883

B,C,D

Measured

Unit

method

Min

Max

terminal

Test no.

CLR 1

D1

CLK 1

PRE 1

Q1

GND

Q2

PRE 2

CLK 2

D2

CLR 2

Q1

Q2

VCC

10

Fig. 5

124, 145

55

MHz

fMAX

TC = +125C

Fig. 4

126-129

2.0

10.0

ns

tPLH1

Fig. 5 8/

130-133

"

16.0

"

Same tests and terminal conditions as subgroup 9, except TC = +125C and limits are as shown.

tPLH2

Fig. 5 8/

134-137

"

13.0

"

tPHL2

Fig. 5

138-141

"

19.0

"

tPHL3

Fig. 4

142-145

"

12.5

"

tPHL4

tSETUP

8/

Fig. 5

146-149

(H)

tSETUP

"

150-153

"

(L)

t(HOLD)

"

154-157

"

(H)

t(HOLD)

"

158-161

"

(L)

11

Same tests, terminal conditions, and limits as for subgroup 10, except TC = -55C.

1/ Cases X and 2 terminals not designated are NC.

2/ C = Normal clock pulse.

D = Momentary connection: 5.0 V to GND to 5.0 V (for subgroup 9, 10, 11. D occurs prior to their input pulses).

E = Data input connected to Q output.

F = Normal input conditioning is 5.0 V, however, momentary logic "0" may be applied for synchronizing test equipment for preconditioning the device.

3/ For circuit B, IOS(max) is 110 mA.

4/ Only a summary of attributes data is required.

5/ Inputs: A = 2.4 V minimum, B = 0.4 V.

6/ Outputs: H ≥ 1.5 V, L ≤ 1.5 V.

7/ fMAX, minimum limit specified is the frequency of the input pulse. The output frequency shall be one-half of the input frequency.

8/ SETUP and HOLD time functionality may be verified by separate tests from propagation delay tests, by monitoring the output at

specified SETUP and HOLD conditions (see fig. 5).

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |