|

|||

|

Page Title:

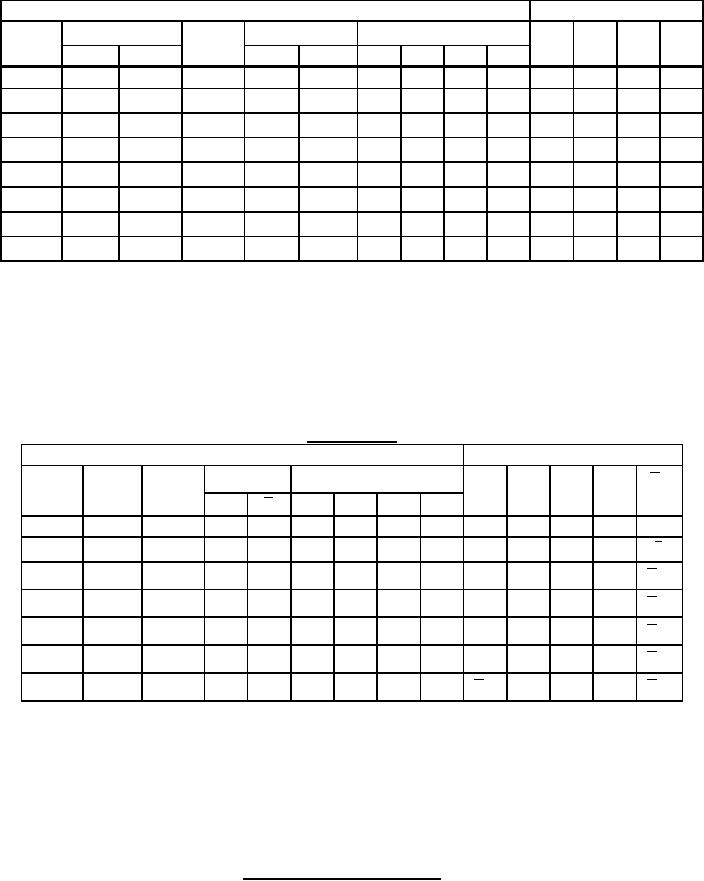

Figure 2. Truth tables and timing diagrams device type 05 |

|

||

| ||||||||||

|

|  MIL-M-38510/9E

Device type 05

INPUTS

OUTPUTS

CLEAR

MODE

CLOCK

SERIAL

PARALLEL

QB

QC

QD

QA

S1

S0

LEFT

RIGHT

A

B

C

D

L

X

X

X

X

X

X

X

X

X

L

L

L

L

H

X

X

L

X

X

X

X

X

X

QB0

QC0

QD0

QA0

X

X

a

b

c

d

a

b

c

d

H

H

H

↑

X

H

X

X

X

X

H

H

L

H

↑

QBn

QCn

QAn

X

L

X

X

X

X

L

H

L

H

↑

QBn

QCn

QAn

H

H

X

X

X

X

X

H

H

L

↑

QCn

QDn

QBn

L

L

X

X

X

X

X

H

H

L

↑

QCn

QDn

QBn

H

L

L

X

X

X

X

X

X

X

QA0 QB0 QC0 QD0

H = high level (steady state), L = low level (steady state), X = irrelevant (any input including transitions)

↑ = transition from low to high level.

a, b, c, d = the level of steady state input at inputs A, B, C, or D, respectively.

QA0, QB0, QC0, QD0 = the level of QA, QB, QC or QD respectively, before the indicated steady state input

conditions were established.

QAn, QBn, QCn, QDn = the level of QA, QB, QC or QD respectively, before the most recent ↑ transition of the

clock.

Device type 06

INPUTS

OUTPUTS

CLEAR

SHIFT/

CLOCK

SERIAL

PARALLEL

QB

QC

QD

QA

QD

LOAD

J

A

B

C

D

K

L

X

X

X

X

X

X

X

X

L

L

L

L

H

H

L

X

X

a

b

c

d

a

b

c

d

↑

d

H

H

L

X

X

X

X

X

X

QBO

QC0

QD0

QA0

QD0

L

H

X

X

X

X

H

H

↑

QA0

QBn

QCn

QA0

Q Cn

H

H

L

L

X

X

X

X

L

↑

QBn

QCn

QAn

Q Cn

H

H

H

H

X

X

X

X

H

↑

QBn

QCn

QAn

Q Cn

H

L

X

X

X

X

H

H

↑

QAn

QBn

QCn

QAn

Q Cn

H = high level (steady state), L = low level (steady state), X = irrelevant (any input including transitions)

↑ = transition from low to high level.

a, b, c, d = the level of steady state input at inputs A, B, C, or D, respectively.

QA0, QB0, QC0, QD0 = the level of QA, QB, QC or QD respectively, before the indicated steady state input

conditions were established.

QAn, QBn, QCn, QDn = the level of QA, QB, QC or QD respectively, before the most recent ↑ transition of the

clock.

Figure 2. Truth tables and timing diagrams Continued.

15

|

|

Privacy Statement - Press Release - Copyright Information. - Contact Us |